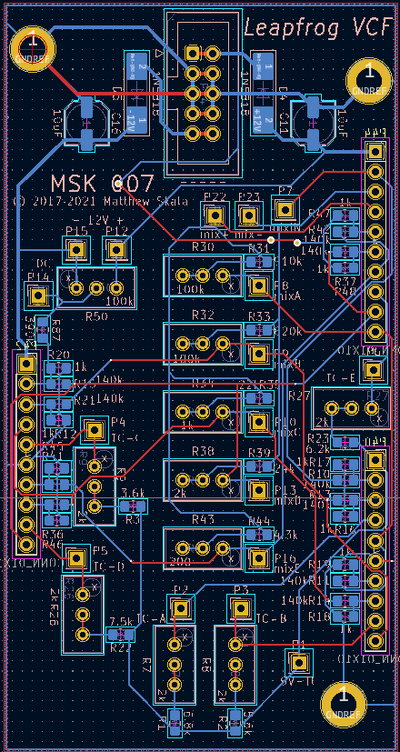

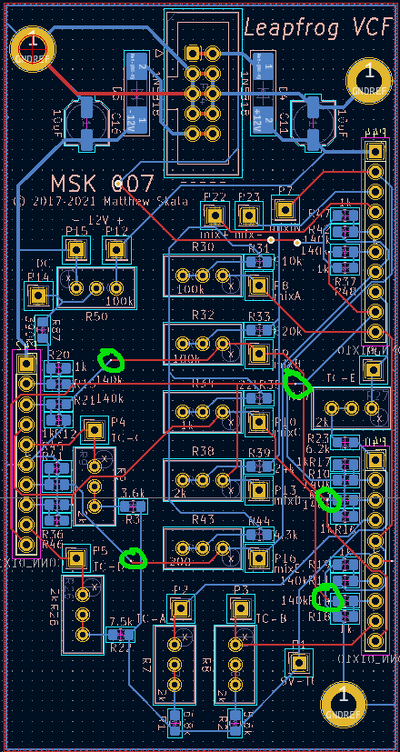

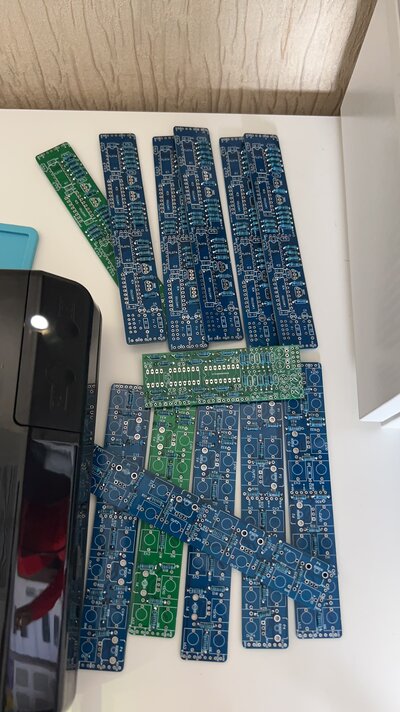

Die markierten sind welche nur ziemlich Kleine:

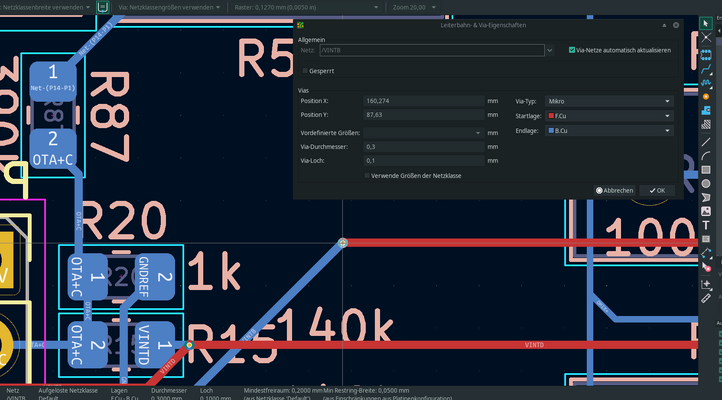

Ähmm darf man fragen warum? Da ist doch massig Platz. Solche winzigen VIA Bohrungen benutzt man eigentlich nur beim Fan-Out von BGA mit 0,5mm Pitch und weniger. Man muss sich immer klar machen das um so feiner die Strukturen werden, umso höher ist die Fehleranfälligkeit der Platinen und deren Herstellung. Hier merkt man dann den Unterschied: Bei JLCPCB wird sowas einfach durch die Anlage geschoben und gehofft das es passt, wenn du das so zu AISLER gibst, dann darfst du direkt nen Aufpreis für engere Fertigungstoleranzen zahlen.

Da ist alles wie das Programm ausgeliefert wurde.

KiCad weis aber nicht, welchen Fertiger du benutzt

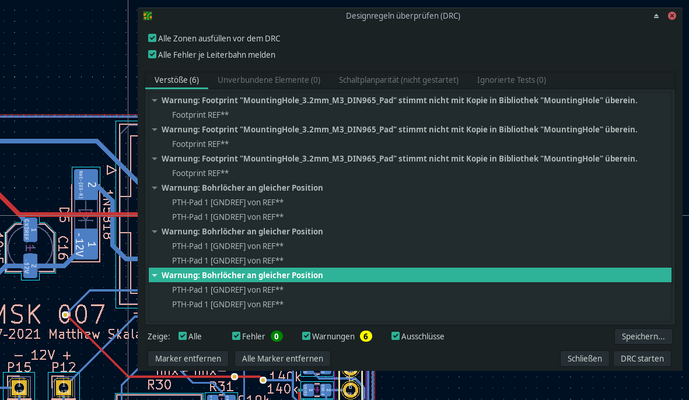

Normalerweise geht man so vor, das man sich auf der Webseite des Fertigers die Fähigkeiten anschaut und darauf basieren die DRC Regeln auf sinnvolle Werte einstellt. Wenn man z.B. mal auf die Seite von JLCPCB geht (

https://jlcpcb.com/capabilities/pcb-capabilities) dann steht da bei 2-Lagenplatine: "Minimum Via Hole Size 0,3mm". Erstaunlich das die 0,1mm Bohrung bei denen durch die Fertigung ist. Könnte sein, das die die VIA in der Vorverarbeitung vergrößert haben?

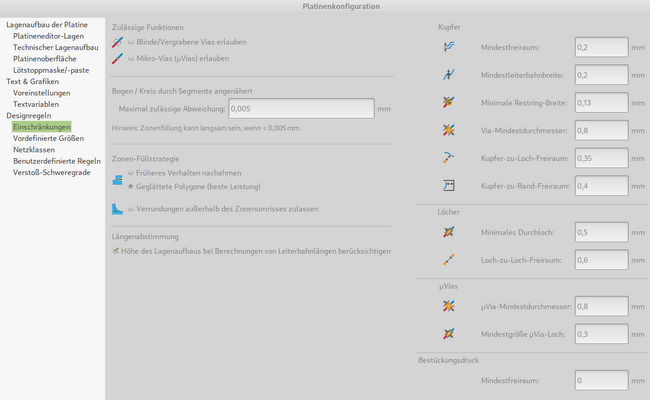

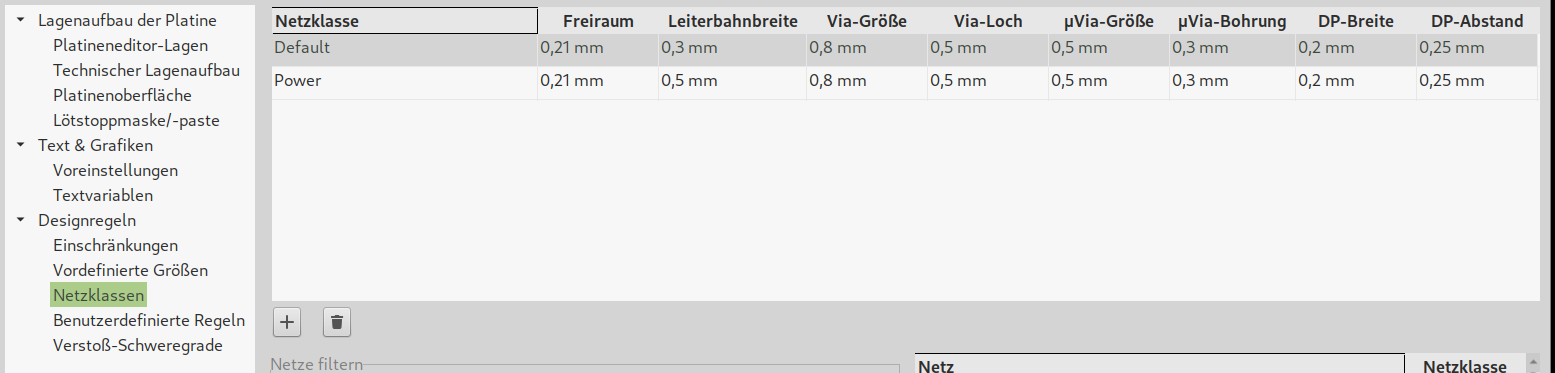

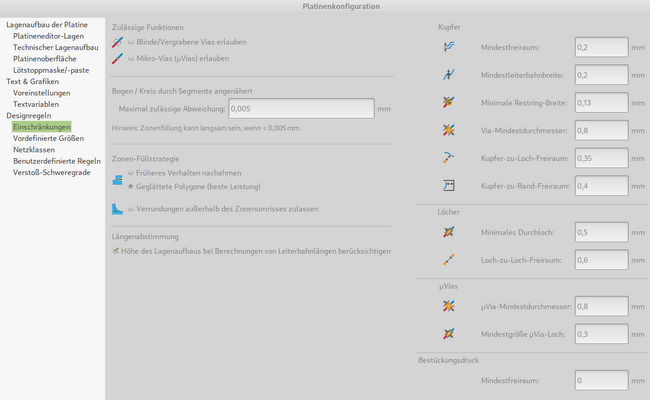

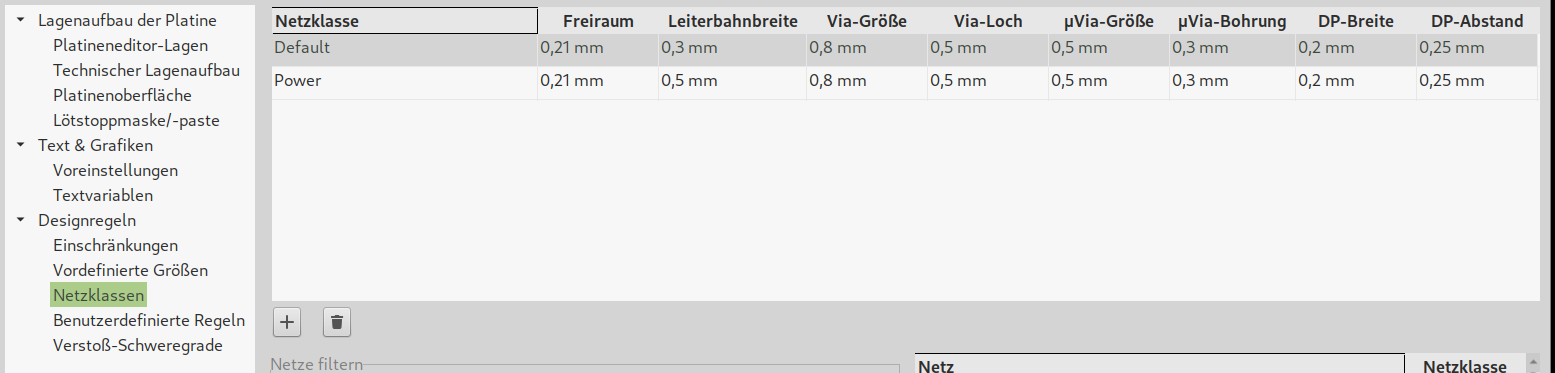

Für Alltags 2-Layer-Platinen stelle ich Kicad normalerweise wie folgt ein:

Das reicht locker für 0603 SMD oder 0,65mm Pitch TSSOP. Mit diesen Werten bleibt noch viel Luft für die Fertigung, man muss nicht unnötig kleine Strukturen machen. Wenn man nicht bis an die Limits geht, kann man sein Platine auch mal problemlos bei anderen Fertigern machen lassen. Bei AISLER bekommt man eine gute Vorstellung davon, was "kompliziert" in der Fertigung ist:

AISLER’s PCB Design Rules Last Updated: 13/05/2024 Design Rules The Design Rules for the individual PCB configurations can be found here: 2 Layer Simple Design Rules (2 Layer Blitz/ Budget) 2 Layer HD Design Rules (2 Layer HD) 4 Layer HD Design Rules (4 Layer HD) 4 Layer 0.8mm Design Rules...

community.aisler.net

Siehe PDF im Anhang.

Siehe PDF im Anhang.